FPGA 实现SVPWM调制

SVPWM调制方法使用 SPWM 零序注入法来实现 SPWM 等效SVPWM (使用最大最小法)

clear;clc;t=0:1e-4:20e-3;va=sin(2*pi*50*t);vb=sin(2*pi*50*t-2*pi/3);vc=sin(2*pi*50*t-4*pi/3);tpos=zeros(1,length(t));tneg=zeros(1,length(t));for i=1:length(t)tpos(i)=max([va(i),vb(i),vc(i)]);tneg(i)=min([va(i),vb(i),vc(i)]);endtriplen=(tpos+tneg)*0.5;va3 = va-triplen+1;vb3 = vb-triplen+1;vc3 = vc-triplen+1;plot(t,va3,t,vb3,t,vc3,t,triplen)

为了简化设计直接使用逻辑资源初始化sin表 为简单化,这里不放正弦表

module svm(input sys_clk,inputrst_n ,output reg [7:0]a,outputreg [7:0]b,output reg [7:0]c);parameter SINN = 12'd1024;reg [7:0] max;reg [7:0] min;reg [7:0] sin[1024:0];reg [11:0] ai;reg [11:0] bi;reg [11:0] ci;//最大值always@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)max <= 8'd0;else if(sin[ai]>=sin[bi])begin if(sin[ai]>=sin[ci])max <= sin[ai];else max <= sin[ci];end else if(sin[bi]>=sin[ci])max <= sin[bi];else max <= sin[ci];//最小值always@(posedge sys_clk or negedge rst_n)if(rst_n==1'b0)min <= 8'd0;else if(sin[ai]<=sin[bi])begin if(sin[ai]<=sin[ci])min <= sin[ai];else min <= sin[ci];end else if(sin[bi]<=sin[ci])min <= sin[bi];else min <= sin[ci];// A 注入零序always@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)a <= 8'd0;elsea <= sin[ai] - (max+min)/2 + 127;// B 注入零序always@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)b <= 8'd0;elseb <= sin[bi] - (max+min)/2 + 127;// C 注入零序always@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)c <= 8'd0;elsec <= sin[ci] - (max+min)/2 + 127;// A sin表Indexalways@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)ai <= 12'd0;else if(ai == SINN-1)ai <= 12'd0;else ai <= ai + 1'b1;// B sin表Indexalways@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)bi <= 12'd341; //B与A 相差120° 1024/3else if(bi == SINN-1)bi <= 12'd0;else bi <= bi + 1'b1;// C sin表Indexalways@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)ci <= 12'd682; C与A 相差240° 1024*2/3else if(ci == SINN-1)ci <= 12'd0;else ci <= ci + 1'b1;//初始化正弦表always@(posedge sys_clk or negedge rst_n)if(rst_n == 1'b0)beginsin[0] <= 127; sin[1] <= 127; sin[2] <= 128; sin[3] <= 129; sin[4] <= 130; sin[5] <= 130; sin[6] <= 131; sin[7] <= 132; sin[8] <= 133; sin[9] <= 134; sin[10] <= 134; sin[11] <= 135; sin[12] <= 136; sin[13] <= 137; sin[14] <= 137; sin[15] <= 138; sin[16] <= 139; sin[17] <= 140; sin[18] <= 140; sin[19] <= 141; sin[20] <= 142; sin[21] <= 143; sin[22] <= 144; sin[23] <= 144; sin[24] <= 145;

仿真文件

`timescale 1ns/1psmodule svm_tb();reg sys_clk;reg rst_n;wire [7:0] a;wire [7:0] b;wire [7:0] c;initialbeginsys_clk <= 1'b1;rst_n <= 1'b0;#80rst_n <= 1'b1;end always #10 sys_clk <= ~sys_clk;svm svm_inst(.sys_clk(sys_clk),.rst_n (rst_n),.a(a),.b(b),.c(c));endmodule

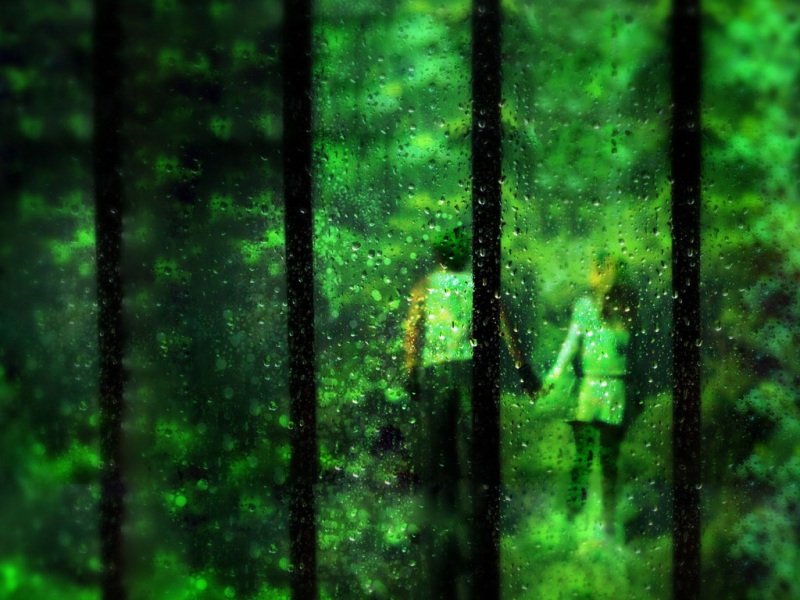

仿真结果

如果觉得《FPGA 实现SVPWM调制》对你有帮助,请点赞、收藏,并留下你的观点哦!